Lunar Lake是英特尔继Meteor Lake和酷睿Ultra之后,被称为重塑人们对X86产品认知的一款处理器。“Lakefield率先尝试了3D封装技术,并且在Meteor Lake上实现了大规模量产。而Meteor Lake是真正意义上实现了CPU+GPU+NPU的多引擎AI加速处理器。”英特尔技术专家在会中提到:“Lunar Lake是全方位创新的新一代平台, CPU性能核和能效核采用了全新的微架构,综合AI性能可以达到120p TOPS(每秒兆次浮点运算)。”

120 TOPS换算下来,每秒钟大约可以进行120万亿次浮点运算的能力。这个概念就像是人一秒钟能做1道数学题,算力120 TOPS则相当于计算机一秒钟能做120万亿道数学题。这样的算力可以让计算机更快地分析数据,并且会提供更精确的结果。

不过,值得注意的是, 120 TOPS是将Lunar Lake的GPU、CPU、NPU所有XPU加一起共为Lunar Lake平台提供高达120 TOPS。划分下来,每个XPU所承担的算力都有不同,同时其责任也各不相同。因此,关于总计120TOPS的混合架构芯片,还是有许多的问题,比如其中不同架构的又与上代产品Meteor Lake有何区别? AI性能的提升,会带来哪些变化?此外,GPU+CPU+NPU三种架构的集合,会对工艺有什么要求?更为重要的是,不同的架构提供了多少TOPS?等。要想回答上述问题,还需要从Lunar Lake的架构说起来。

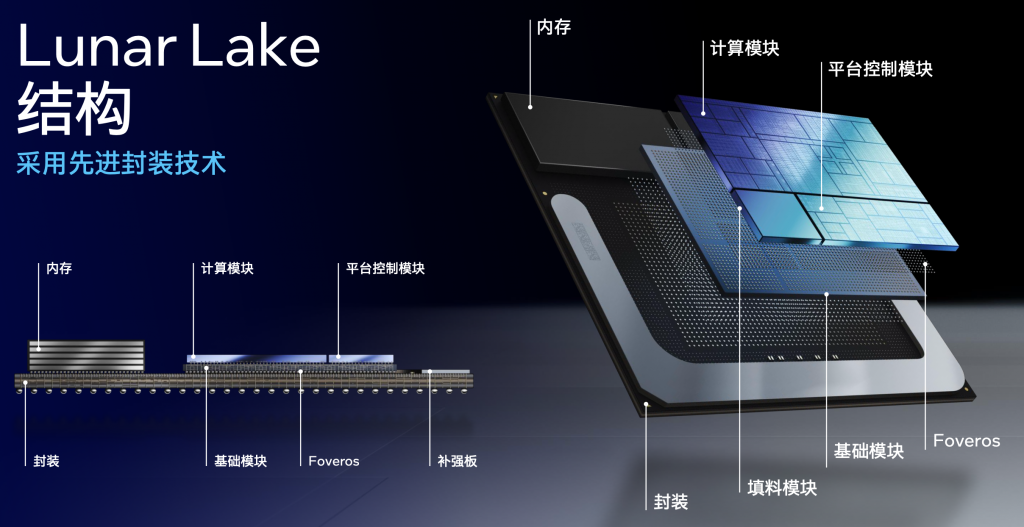

紧凑“有型”的Lunar Lake架构

Lunar Lake采用了LPDDR5X 内存芯片集成于处理器封装之上的封装技术,MoP(Memory on Package)封装。这将会提高系统的整体性能和效率,因为集成内存可以减少数据传输的延迟,并支持更高的数据吞吐量,除此之外,还节省了250mm平方的面积,从而使得PCB的层数能够降低,紧凑的主板设计使面积变少。相应的,在显著的好处之外,也会涉及到许多复杂的技术和设计挑战,例如功耗管理问题,特别是在高性能应用中,同时内存与处理器核心和设计之间的布线必须非常精准,以确保信号的速度和稳定性。

在英特尔的MoP技术之前,一些内存封装在SoC的芯片,多用于移动端。为了降低功耗实现高性能,大多数都是采用了水平堆叠的多层封装,例如A14、A15以及高通骁龙888和8Gen1等等。而用于高性能、数据中心或者更直白一些来说,用于PC端(无论是笔记本还是台式)的封装在SoC内存,Lunar Lake是首款, 内存规格为LPDDR5x。至多可设计2颗内存颗粒,至多支持的内存内容为32GB。而为了集成了所有平台的控制器,包括安全的组件、以及无线/有线的连接组件,英特尔利用3D Foveros封装技术将两不同模块封装在一个无源的基衬上,从而实现了紧凑的Lunar Lake芯片。

整体的架构含有Lion Cove的P核,Skymont的E核以及Xe2的GPU微架构,以及第四代NPU。Lunar Lake计算芯片支持4个p核、4个E核。由于去掉了P-core的超线程设计,最终所呈现的将是8核心8线程的混合架构规格。集显单元英特尔为之换上了崭新的微架构Xe2,它提供了8个Xe核,同时还有8个光线追踪单元。在XPU的战略宣布之后,英特尔加大了PC处理器极限引擎的开发和迭代。作为崭新的微架构Xe2,使命即是为AI提供推理性能的加持,这就导致,整个Lunar Lake架构的AI算力集中在了GPU单元中,达到了67 TOPS。

同样,在XPU战略进程中,AI先行的理念,NPU则是英特尔在AI加速器持续投入的产物。最新一代的NPU相较于前代Meteor Lake,提升了大概有4倍NPU计算能力,达到48 TOPS。这得益于其中有6个NPU引擎,共有9MB片上缓存,来加持在低功耗下持续的AI算力。并且NPU还包括12个Enhanced SHAVE,这个SHAVE是其中的一种DSP,主要用途是来做向量计算的,现总共有12个增强型的SHAVE DSP功能。

英特尔技术相关人员介绍说,Lunar Lake的新的CPU性能核和能效核采用了全新的微架构,能效比提升40%,在相同的单线程情况下,Lunar Lake可以节省一半功率。而采用全新的图形引擎,在性能提升1.5倍。其AI性能也大幅度提升,综合AI性能可以达到120 p TOPS以上,此外先进的3D封装以及片上内存的设计可以让OEM设计出更优美和更轻薄的笔记本产品。

多面创新,构建P核心性能

Lunar Lake的整体构架已经比较熟悉,结合Lion Cove的P核、Skymont的E核以及Xe2的GPU微架构,Lunar Lake实现了多种不同处理器单元的有效结合。这种设计不仅提升了性能,还进一步优化了功耗。因此,Lunar Lake在计算性能上展现出显著的改变,特别是在多引擎AI加速方面,使得处理器在执行不同环境中的任务时会更加高效。

其中,Lion Cove的P核做出了重大的改变。为了使Lunar Lake具有高能效,会去除任何对最终产品没有贡献的晶体管,而超线程在Lunar Lake上,只是被移除的功能之一。英特尔技术专家解释道,在最初的设计选择上,超线程是一个选择题,选择是的情况下,在相同芯片面积下,可以增加30%的IPC,代价是多20%的功耗。在动态电容(Dynamic Capacitance)的参考下,在电压频率不变的情况下,功耗上升20%,但能带来30%的性能增加。

这也就是说,在追求线程密度时,比如说数据中心部署中,超线程是非常好的选择,或者说是目前最佳的选择。但在客户端SoC方面,情况会截然不同,由于引入的是高性能混合架构核心,同时具备P核和E核。在近几代芯片中,E核已经被证明是比超线程更高效的一种多线程加速手段。所以,英特尔在考虑P核与E核的设计时,想到如果要追求多线程性能的话,与其去赋能超线程,不如去做E核。

因此,英特尔技术专家特别强调道,P核是单线程的,而且只有单线程,没有超线程,不会也不能去赋能超线程。除此之外,P核在能效管理方面,也做足了改变——引入了动态的,基于AI神经网络的AI Self-tuning controller(AI自调节控制器,即一种利用人工智能技术自动调整自身参数以优化性能的控制系统。)。使P核能够根据实际的平台实时的温度、环境,去设置适当的时间阈值,以贴合当下环境的温度收敛曲线。

更加精细的效能管理之下,英特尔还引入了更加精细的频率调节。在Lion Cove架构中,每个频率步长缩小到了16.67MHz,这就意味着用户可以更精细地调整CPU频率。比如,最高频率是3.08GHz,但实际达不到时,可以降到比3.08GHz稍低的频率,不是降到3.0GHz,而是3.067GHz,这样又挤出来了2%的性能。

在微架构设计方面,英特尔技术专家特别提到,P核微架构的改革,彻底实现了性能的提升,同时消除了里面的结构性障碍,为后面几代P核奠定设计基础。首先,是从前端获取指令,进行Decode(指令解码),采用的是Wider Machine(在计算机体系结构中,通常指的是通过增加处理单元的数量和并行处理能力来提高处理器性能的设计理念。)设计概念,增加了8倍宽度的Prediction区块(Prediction block,预测处理器即将执行的指令或数据。)以及2倍的Fetch区块(Fetch Block, 从内存或缓存中获取即将执行的指令),周期的取指字节数从64字节增加到128字节。其次,Decode的BW(Bandwidth,缓存读取的带宽)也由原来的6,提高到了现在的8。最后,技术专家介绍道,这其中微架构的Cache(缓存)极其重要,因此,缓存容量从4K增长到了5.25K;读取的BW也增加了50%;微操作队列的数目也有所增加,由原来的144变为了192。

乱序执行引擎(Out-of-Order Execution Engine)在P核中也是一个创新点。英特尔将乱序执行引擎分成了两个独立的域:整数(INT)域和向量(VEC)域。与以往相比较,不需要一个统一的调度器来处理所有类型的操作,并且还为每个域配置专用的调度器,简化了调度器设计,减少了硬件开销,提高了处理器的性能和能效。这种设计能够更高效地处理不同类型的操作,减少资源争用和能量消耗,是一种重要的微架构创新。

另外,英特尔又重新设计了内存子系统。前一代Redwood Cove,CPU绑定在每个P核内的缓存是两层,分别是L1和L2。但是在Lion Cove中,则增加了三层缓存分别是L0 Cache(新增的第一层缓存,大小为48KB。)、L1 Cache(中间层缓存,大小为192KB,插在原来的L1和L2之间。)以及L2 Cache(MLC Cache,2.5MB,每个P核独立的二级缓存。),再加上共享的一级缓存(总大小为12MB),共有四层Cache。此外,还增加Translation Buffer和AGU模块,提高地址转换和数据访问的效率。这些改进的共同目标是减少内存访问延迟、增加指令执行并行度(IPC),从而提升处理器的整体性能和效率。

全面增强,覆盖日常需求

如果说P核是Lunar Lake的“神兵”,常用于极端重载的情况下,那么E核则是Lunar Lake的“利器”,以尽可能的覆盖更多的日常计算需求为主导方向,来尽可能降低P核的使用机会。

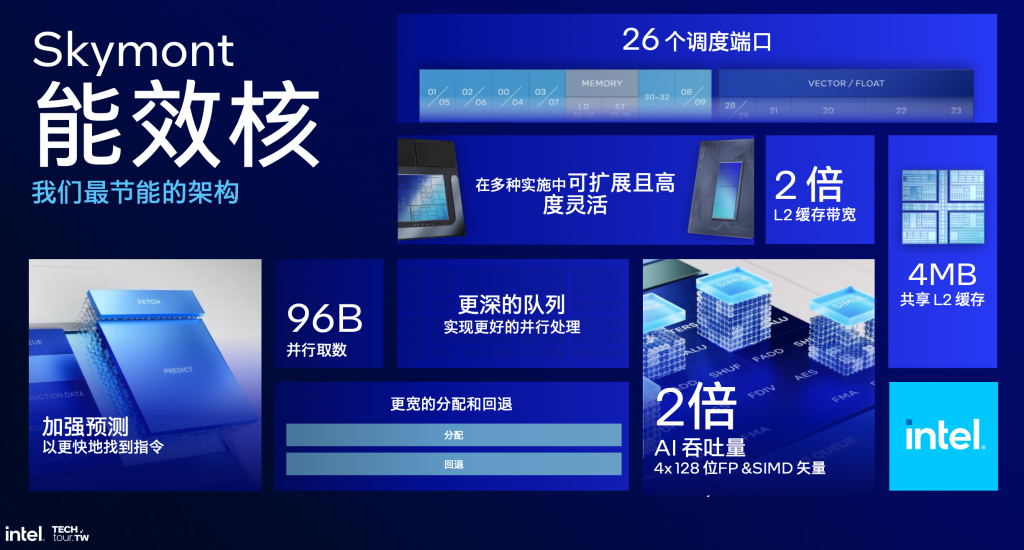

但是值得注意的是,Lunar Lake的Skymont设计参考方向是Raptor Lake的P核性能,英特尔甚至希望能够保持与其E核级别的能效水平。这就意味着Skymont会更加强调更宽的Wider Machine,并且还要致力于提高核内并行性的处理能力,然后去优化能耗。

在Predict中,相较于前一代的微架构,Skymont的改进由每个时钟周期内的64字节的预测,提升到了128字节,处理器从缓存读取数据的带宽增加了50%。Prediction Across能力翻倍,使得处理器架构更加宽泛,可以更快的进行查找和分发工作。在Decode方面,相比前一代提高了50%,这也就意味着每个时钟周期可以解码9条X86指令。此外,UOP队列的容量从前一代的64提高到了96个条目。同时,Skymont还引入了Nanocode新功能,它是允许每一个解码集群可以独立去处理多个microcode流,也是为了大大提高并行性能。

而在乱序执行方面,地址和重命名的宽度从6增加到8,每周期退出指令从8增加到16。并且引入了Dependency breaking,用以减少指令间的依赖,降低延迟。还提升了ROB容量,从256增加到416,增加了60%。后端资源方面,Physical register files、Load&store buffer和reservation stations能够又机会放到冗余里面,拿来执行。值得一提的是,Skymont微架构分发方面也有很多的执行资源,比如说上一代E核每周期分发17个,现在每周期可以分发26个。同时8个整数的ALU指令是可以同时被支持的,每周期可以处理3个跳转,这些都提升了并行处理能力。

再聊一些细节,浮点和矢量的运算能力,Skymont有4个完整的端口,也就是说4个128bit的ALU和Vector,用于指令VNNI的指令,使得gigaflops和TOPS都翻倍。而其他的执行单元本身,像FADD、FMA,也都重新进行了设计,以达到降低延迟的目标。另外,Load/Store Enhancements(加载/存储增强)方面,Memory地址翻译的时候,Strore从L1的translation buffer读取带宽增加了50%,从2个变成3个128bit的。同时生成存储地址的能力也翻倍了,也就是说当L1 Translation Buffer未能命中时,需要从更高级的缓存(如L2缓存)中查找翻译信息,而L2缓存的容量从3K增加到4K,Strore从L1的translation buffer读取带宽增加了50%,从2个变成3个128bit的。更大的L2缓存容量意味着更多的地址翻译信息可以被缓存,提高了命中率,减少了访问主存的次数,提高了整体内存访问的效率。

性能方面,与Meteor Lake LP E核做比较,PC的性能有38%的整数性能提升,68%的浮点性能的提升。能耗方面,用1/3的功耗能便可以获得和Crestmont一样的性能。在Lunar Lake上还有一个特殊设计,它的PowerVia for E Core是独立的,所以可以让Lunar Lake的频率跑得更高,把这些因素加总在一起,最终性能Skymont可以达到Meteor Lake LP E核的两倍。

写在最后:

Lunar Lake处理器通过全面的架构优化和技术创新,实现了显著的性能提升。P核和E核的设计改进,使得处理器在执行复杂任务时更加高效,同时大幅提升了AI性能和整体计算能力。总体来看,Lunar Lake通过多面创新,构建了高效能和高性能的处理器平台,满足了日常计算需求到高负载任务的广泛应用场景。它不仅展示了英特尔在技术上的创新在不断的地位,也为未来的计算平台设立了新的标杆。

京公网安备 11010202008829号

京公网安备 11010202008829号